Berkeley Lab announces first transistor with a working 1-nanometer gate

October 11, 2016

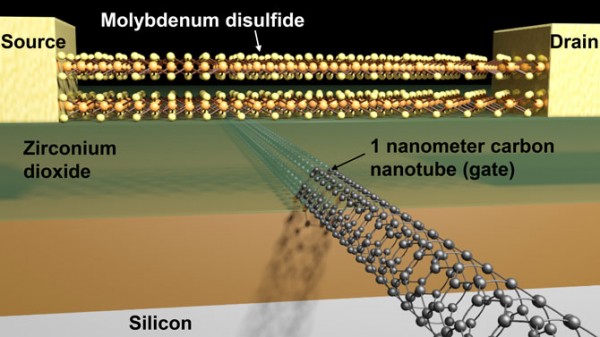

Schematic of a transistor with molybdenum disulfide semiconductor and 1-nanometer carbon nanotube gate. (credit: Sujay Desai/Berkeley Lab)

The first transistor with a working 1-nanometer (nm) gate* has been created by a team led by Lawrence Berkeley National Laboratory (Berkeley Lab) scientists. Until now, a transistor gate size less than 5 nanometers has been considered impossible because of quantum tunneling effects. (One nanometer is the diameter of a glucose molecule.)

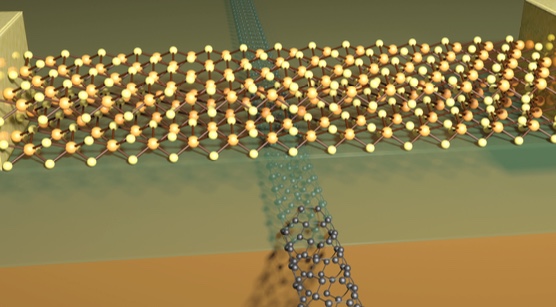

The breakthrough was achieved by creating a 2D (flat) semiconductor field-effect transistor using molybdenum disulfide (MoS2) instead of silicon and a 1D single-walled carbon nanotube (SWCNT) as a gate electrode, instead of various metals. (SWCNTs are hollow cylindrical tubes with diameters as small as 1 nanometer.)

The MoS2 advantage

Compared with MoS2, electrons flowing through silicon are lighter and encounter less resistance . But with a gate length below 5 nanometers in length, a quantum mechanical phenomenon called tunneling kicks in, and the gate barrier is no longer able to keep the electrons from barging through from the source to the drain terminals, so the transistor cannot be turned off.

Electrons flowing through MoS2 are heavier, so their flow can be controlled with smaller gate lengths. MoS2 can also be scaled down to atomically thin sheets, about 0.65 nanometers thick, with a a larger band gap and lower dielectric constant, a measure reflecting the ability of a material to store energy in an electric field (similar to a capacitor). These properties help improve the control of the flow of current inside the transistor when the gate length is reduced to 1 nanometer.

Transistors consist of three terminals: a source (left), a drain (right), and a gate (the carbon nanotube, black, below). Current flows through the semiconductor (MoS2, represented by the yellow molecular model) from the source to the drain. Based on the voltage applied to the gate, it switches the channel (the portion of the MoS2 semiconductor just above the carbon nanotube) on and off, via a dielectric (zirconium oxide, green), operating in a manner similar to a capacitor. (credit: Sujay Desai/Berkeley Lab)

“We made the smallest transistor reported to date,” said faculty scientist Ali Javey at the Department of Energy’s Lawrence Berkeley National Laboratory (Berkeley Lab) and lead principal investigator of the Electronic Materials program in Berkeley Lab’s Materials Science Division. “The gate length is considered a defining dimension of the transistor. We demonstrated a 1-nanometer-gate transistor, showing that with the choice of proper materials, there is a lot more room to shrink our electronics.”

The development could be key to keeping alive Intel co-founder Gordon Moore’s prediction that the density of transistors on integrated circuits would double every two years, enabling the increased performance of our laptops, mobile phones, televisions, and other electronics.

“The semiconductor industry has long assumed that any gate below 5 nanometers wouldn’t work, so anything below that was not even considered,” said study lead author Sujay Desai, a graduate student in Javey’s lab. “This research shows that sub-5-nanometer gates should not be discounted. Industry has been squeezing every last bit of capability out of silicon. By changing the material from silicon to MoS2, we can make a transistor with a gate that is just 1 nanometer in length, and operate it like a switch.”

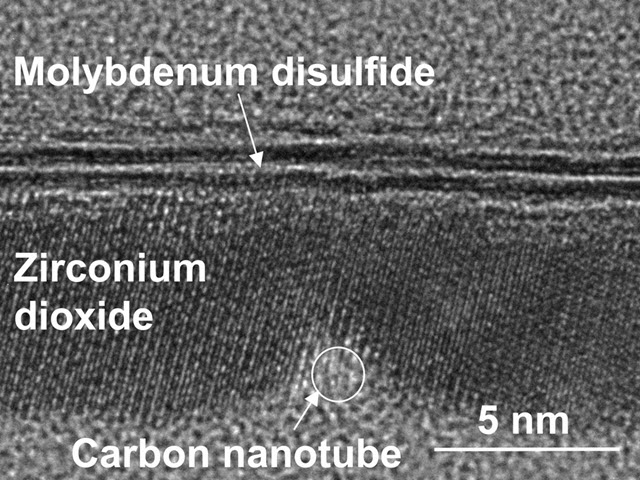

Transmission electron microscope image of a cross section of the transistor, showing the edge of a 1-nanometer carbon nanotube gate and the molybdenum disulfide semiconductor separated by zirconium dioxide, which is a dielectric insulator. (credit: Sujay B. Desai/Science)

Continuing Moore’s law

“This work demonstrated the shortest transistor ever,” said Javey, who is also a UC Berkeley professor of electrical engineering and computer sciences. “However, it’s a proof of concept. We have not yet packed these transistors onto a chip, and we haven’t done this billions of times over. We also have not developed self-aligned fabrication schemes for reducing parasitic resistances in the device. But this work is important to show that we are no longer limited to a 5-nanometer gate for our transistors. Moore’s Law can continue a while longer by proper engineering of the semiconductor material and device architecture.”

The findings appeared in the Oct. 7 issue of the journal Science. Researchers at the University of Texas at Dallas, Stanford University, and the University of California, Berkeley, were also involved. The work at Berkeley Lab was primarily funded by the Department of Energy’s Basic Energy Sciences program.

According to an earlier article in CTimes on Sept. 30, Taiwan Semiconductor Manufacturing Co., Ltd. (TSMC) said the company is working toward a 1-nanometer manufacturing process, starting with a “5 nanometers process technology, while putting about 300 to 400 R&D personnel in developing more advanced 3-nanometer process.” However, TSMC spokesperson Elizabeth Sun told KurzweilAI that “no further information regarding any technology either under development or in path-finding stage will be disclosed to the public at this point.”

* Gate length is the length of the gate portion of the transistor, not to be confused with “node,” which was initially a measure of “half pitch” (half of the distance between features of a transistor), but the number itself has lost the exact meaning it once held. Gate length was 26nm for the 22nm node from Intel and 20 nanometers for the more recent 14nm node from Intel. — S. Natarajan et al., “A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size,” 2014 IEEE International Electron Devices Meeting, San Francisco, CA, 2014, pp. 3.7.1-3.7.3. doi: 10.1109/IEDM.2014.7046976

Abstract of MoS2 transistors with 1-nanometer gate lengths

Scaling of silicon (Si) transistors is predicted to fail below 5-nanometer (nm) gate lengths because of severe short channel effects. As an alternative to Si, certain layered semiconductors are attractive for their atomically uniform thickness down to a monolayer, lower dielectric constants, larger band gaps, and heavier carrier effective mass. Here, we demonstrate molybdenum disulfide (MoS2) transistors with a 1-nm physical gate length using a single-walled carbon nanotube as the gate electrode. These ultrashort devices exhibit excellent switching characteristics with near ideal subthreshold swing of ~65 millivolts per decade and an On/Off current ratio of ~106. Simulations show an effective channel length of ~3.9 nm in the Off state and ~1 nm in the On state.