UCLA develops scalable method of fabricating high-speed graphene transistors

June 20, 2011

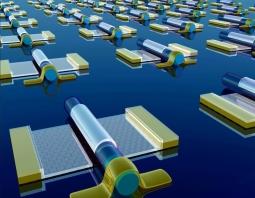

Researchers at the Nanoelectronics Research Facility and the Center for High Frequency Electronics at the University of California, Los Angeles have developed a scalable approach to fabricating high-speed graphene transistors.

This represents a significant advance toward graphene-based, radio-frequency circuits that could be used in a variety of devices, including radios, computers, and mobile phones. The technology might also be used in wireless communication, imaging, and radar technologies, the researchers said.

Graphene, a one-atom-thick layer of the graphite form of carbon (found in pencil lead), has the potential to make consumer electronic devices faster and smaller. But its unique properties, and the shrinking scale of electronics, has also made graphene difficult to fabricate and to produce on a large scale.

The team used a dielectrophoresis assembly technique to place nanowire gate arrays on large-area chemical vapor deposition (growth graphene as opposed to mechanically peeled graphene flakes) to enable the fabrication of high-speed transistor arrays.

They used a glass substrate to minimize parasitic delay and enable graphene transistors with extrinsic cut-off frequencies exceeding 50 GHz. Typical high-speed graphene transistors are fabricated on silicon or semi-insulating silicon carbide substrates that tend to bleed off electric charge, leading to extrinsic cut-off frequencies of around 10 GHz or less.

The researchers used these graphene transistors to construct radio-frequency circuits functioning up to 10 GHz, a substantial improvement from previous reports of 20 MHz.

Lei Liao, et al., Scalable fabrication of self-aligned graphene transistors and circuits on glass, Nano Letters, 2011; 110607115253088 [DOI: 10.1021/nl201922c]