How to build a full-scale quantum computer in silicon

November 2, 2015

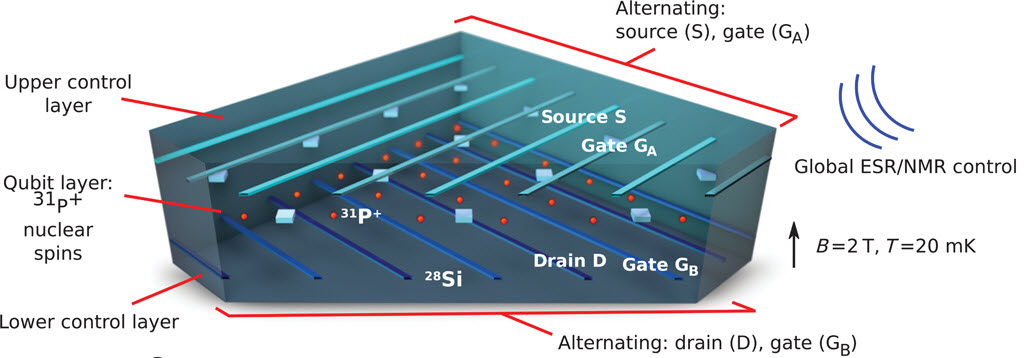

Physical layout of the surface code* quantum computer. The system comprises three layers. The 2D donor qubit array resides in the middle layer. A mutually perpendicular (crisscross) pattern of control gates in the upper and lower planes form a regular 3D grid of cells. (credit: Charles D. Hill et al./Science Advances)

A new 3D silicon-chip architecture based on single-atom quantum bits has been designed by researchers at UNSW Australia (The University of New South Wales) and the University of Melbourne.

The use of silicon makes it compatible with existing atomic-scale fabrication techniques, providing a way to build a large-scale quantum computer.**

The scientists and engineers from the Australian Research Council Centre of Excellence for Quantum Computation and Communication Technology (CQC2T), headquartered at UNSW, previously demonstrated a fabrication strategy. But the hard part in scaling up to an operational quantum computer was the architecture: How to precisely control multiple qubits in parallel across an array of many thousands of qubits and constantly correct for quantum errors in calculations.

The CQC2T collaboration says they have now designed such a device. In a study published Friday (Oct. 30) in an open-access paper in Science Advances, the CQC2T team describes a new silicon architecture that uses atomic-scale qubits aligned to control lines (essentially very narrow wires) inside a 3D design.

UNSW | How to build a quantum computer in silicon

Error correction

Errors (caused by decoherence and other quantum noise) are endemic to quantum computing, so error correction protocols are essential in creating a practical system that can be scaled up to larger numbers of qubits.

“The great thing about this work, and architecture, is that it gives us an endpoint,” says UNSW Scientia Professor Michelle Simmons, study co-author and Director of the CQC2T. “We now know exactly what we need to do in the international race to get there.”

In the team’s conceptual design, they have moved from the conventional one-dimensional array (in a line) of qubits to a two-dimensional array (in a surface), which is far more tolerant of errors. This qubit layer is “sandwiched” between two layers of control wires arranged in a 3D grid.

By applying voltages to a subset of these wires, multiple qubits can be controlled in parallel, performing a series of operations using far fewer controls. They can also perform the 2D surface-code* error correction protocols, so any computational errors that creep into the calculation can be corrected faster than they occur.

The researchers believe their structure is scalable to millions of qubits, and that means they may be on the fast track to a full-scale quantum processor.

* “Surface code is a powerful quantum error correcting code that can be defined on a 2D square lattice of qubits with only nearest neighbor interactions.” — Austin G. Fowler et al. Surface code quantum error correction incorporating accurate error propagation. arXiv, 4/2010

** In classical computers, data is rendered as binary bits, which are always in one of two states: 0 or 1. However, a qubit can exist in both of these states at once, a condition known as a superposition. A qubit operation exploits this quantum weirdness by allowing many computations to be performed in parallel (a two-qubit system performs the operation on 4 values, a three-qubit system on 8, and so on). As a result, quantum computers will far exceed today’s most powerful supercomputers, and offer enormous advantages for a range of complex problems, such as rapidly scouring vast databases, modeling financial markets, optimizing huge metropolitan transport networks, and modeling complex biological molecules.

Abstract of A surface code quantum computer in silicon

The exceptionally long quantum coherence times of phosphorus donor nuclear spin qubits in silicon, coupled with the proven scalability of silicon-based nano-electronics, make them attractive candidates for large-scale quantum computing. However, the high threshold of topological quantum error correction can only be captured in a two-dimensional array of qubits operating synchronously and in parallel—posing formidable fabrication and control challenges. We present an architecture that addresses these problems through a novel shared-control paradigm that is particularly suited to the natural uniformity of the phosphorus donor nuclear spin qubit states and electronic confinement. The architecture comprises a two-dimensional lattice of donor qubits sandwiched between two vertically separated control layers forming a mutually perpendicular crisscross gate array. Shared-control lines facilitate loading/unloading of single electrons to specific donors, thereby activating multiple qubits in parallel across the array on which the required operations for surface code quantum error correction are carried out by global spin control. The complexities of independent qubit control, wave function engineering, and ad hoc quantum interconnects are explicitly avoided. With many of the basic elements of fabrication and control based on demonstrated techniques and with simulated quantum operation below the surface code error threshold, the architecture represents a new pathway for large-scale quantum information processing in silicon and potentially in other qubit systems where uniformity can be exploited.